| Interne differentiële isolatie conversie |  |

| 16-bits resolutie | |

| Nauwkeurigheid: 2 hoekminuten | |

| Vergrendelingsuitgang met drie standen | |

| Hoge continue volgsnelheid | |

| 36-draads zoutmistbestendig metaal verzegeld DDIP-pakket | |

| Pin-To-Pin compatibel met Model SDC14560 van DDC company |

| geïntegreerd conversieapparaat voor continue tracking ontworpen op de | principe van model II servo. Deze serie producten zijn ontworpen en |

| vervaardigd door MCM-proces, nemen de kernelementen een speciale chip aan; | |

| onafhankelijk ontwikkeld door ons instituut. De pin-regeling is: | |

| compatibel met producten uit de SDC14560-serie van het Amerikaanse DDC-bedrijf, 16-bit | |

| parallelle natuurlijke binaire code data-latch-uitgang, 36-lijns DIP totaal | |

| verzegelde metalen verpakking, hebben de voordelen van hoge precisie, klein; | |

| volume, laag stroomverbruik, lichtgewicht en hoge betrouwbaarheid enz., | en kan op grote schaal worden gebruikt in belangrijke strategische en tactische wapens zoals: |

| vliegtuigen, marineschip, kanon, raket, radar, tank, enz. | |

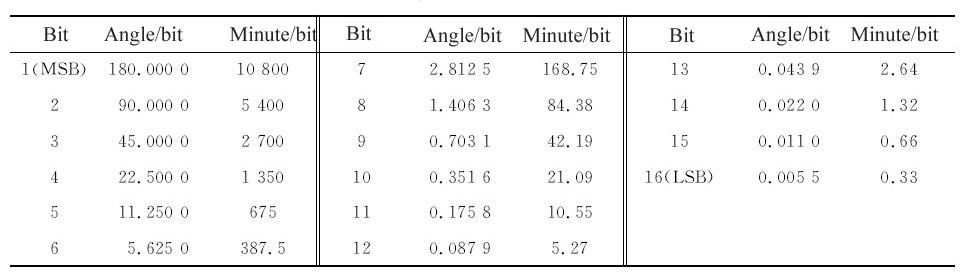

| 4. Elektrische prestaties (tabel 1, tabel 2) | |

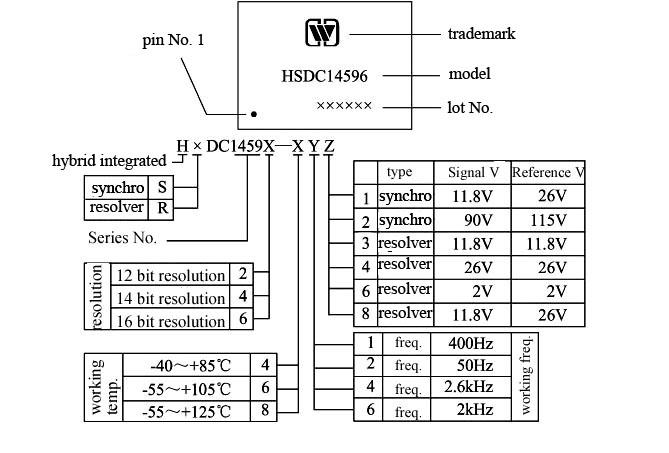

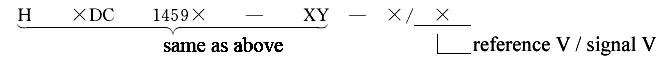

| Synchro naar digitaal converters of resolver naar digitaal converters (HSDC/HRDC1459-serie) | |

| Tabel 1 Nominale voorwaarden en aanbevolen bedrijfsomstandigheden | |

| Absoluut max. nominale waarde |

| Signaalspanning V1: nominale waarde ±20% | Referentiespanning VRef: nominale waarde ±20% | Bedrijfsfrequentie f: nominale waarde ±20% | |

| Opslagtemperatuur Tstg: -65~150℃ | Aanbevolen bedrijfsomstandigheden | ||

| Logische voedingsspanning VL: 5 ± 0,5 V | Voedingsspanning Vs: 15 ± 0,75 V | ||

| Signaalspanning V1: nominale waarde ±10% | Referentiespanning VRef: nominale waarde ±20% | Bedrijfsfrequentie f: nominale waarde ±20% | — |

| Bereik van bedrijfstemperatuur (TA): -55℃~125℃ | Opmerking: * geeft aan dat het kan worden aangepast aan de eisen van de gebruiker. | Tabel 2 Elektrische kenmerken | Parameter |

| Voorwaarden | — | HSDC14569 serie | (VSu003d15V, VLu003d+5V) |

| Militaire standaard (Q/HW20725-2006) | — | 2V | Min. |

| Maximaal | — | Oplossing | Binaire systeem parallelle digitale code |

| 16 bits | — | 2V | Nauwkeurigheid |

| ± 10% van signaalspanning, referentiespanning en fluctuatiebereik van werkfrequentie | — | -2 hoekige minuten | +2 hoekige minuten |

| Bereik van referentiefrequentie: | — | 50Hz | 2600Hz |

| Bereik van referentiespanning: | — | 115V | Referentie ingangsimpedantie |

4.4kΩ 4.4kΩ | — | 0 | 129,2 kΩ |

Bereik van signaalspanning Bereik van signaalspanning | — | 0 | 90V |

Signaal ingangsimpedantie Signaal ingangsimpedantie | — | 0 | 4.4kΩ |

| 102.2 kΩ | — | Signaal/referentie faseverschuiving | —70° |

| +70° | — | Logisch niveau invoer | Logica "1" ≥3,3V |

| Logisch "0" ≤0.8V | — | invoer | 0,8V |

| invoer | — | 0,8V | |

| invoer | — | — | 0,8V |

| Logisch uitvoerniveau | — | — | Logica "1" ≥3,3V |

| Logisch "0" ≤0.8V | — | — | Digitale hoekcode-uitgang |

| Logica "1" ≥3,3V | — | — | Logisch "0" ≤0.8V |

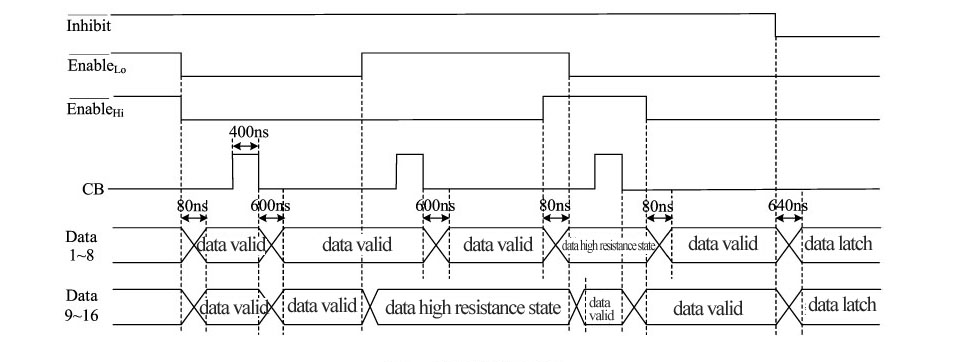

| Bezetsignaal (CB)-uitgang converteren | — | 200ns | 600ns |

| Foutdetectie Bit-output | Logica '0' geeft een fout aan | — | Laadcapaciteit |

| 3TTL | Trackingsnelheid | ||

| 2,5rps | Versnellingsconstante | ||

| +10V Huidig VSu003d+15V 10mA |  VS u003d-15V |

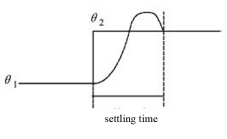

snelheid. Het oscillatieproces van de digitale uitgangshoek wordt getoond in

snelheid. Het oscillatieproces van de digitale uitgangshoek wordt getoond in 6. Werkingsprincipe (Fig. 3)

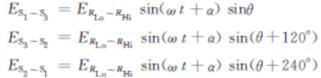

6. Werkingsprincipe (Fig. 3)| Synchro naar digitaal converters of resolver naar digitaal converters (HSDC/HRDC1459-serie) Het ingangssignaal van synchro (of resolver) wordt omgezet in het orthogonale signaal via de interne differentiële isolatie: | |

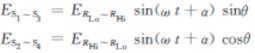

Vcosu003dKE0sin (ωt+α) cosθ (cos)ofWaar, θ is de analoge invoerhoek. Fig.2 Curve van staprespons | Deze twee signalen en de digitale hoek φ van interne omkeerbare tellerof worden vermenigvuldigd met de vermenigvuldiger van sinus- en cosinusfuncties en zijn fout behandeld: |

| versterking, fasediscriminatie en integratiefiltratie, als | θ-φ≠0, de spanningsgestuurde oscillator zal de pulsen uitvoeren, en de | omkeerbare teller telt, totdat θ-φ nul wordt binnen de nauwkeurigheid van | de converter, tijdens dit proces volgt de conversie de verandering van | invoerhoek de hele tijd. | Leesmethode: |

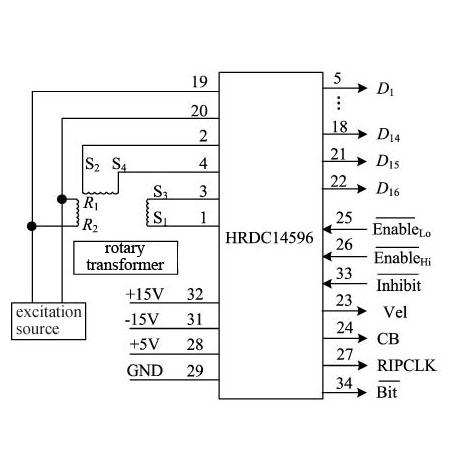

| 1 | S1 | De volgende twee methoden zijn beschikbaar voor gegevensoverdracht: | 25 |  | (1) Remmethode: |

| 2 | S2 | Na 640ns van | 26 |  | logisch laag, de uitvoergegevens zijn geldig en de converter realiseert gegevensoverdracht via: |

| 3 | S3 | en | 27 | . Nadat Inhibit is opgeheven, genereert het systeem automatisch een puls met een breedte die gelijk is aan de bezetpuls voor het bijwerken van gegevens. | (2) Buste-modus: |

| 4 | S4 | Op de stijgende rand van de drukke puls telt de omkeerbare teller met drie standen; aan de dalende rand van de Busy-puls genereert het intern een vergrendelingspuls met een breedte gelijk aan de Busy-puls voor het bijwerken van de gegevens van de driestandenvergrendeling, de tijdreeks van het woord '600' in de andere wordt weergegeven. van Busy-logica laag, is de stabiele overdracht van gegevens geldig. In de asynchrone leesmodus is de drukke uitgang een pulstrein op CMOS-niveau. De breedte van het hoge en lage niveau hangt af van de werkfrequentie en de rotatiesnelheid van het geselecteerde apparaat. | 28 | VL | Fig.4 Tijdsvolgorde van gegevensoverdracht |

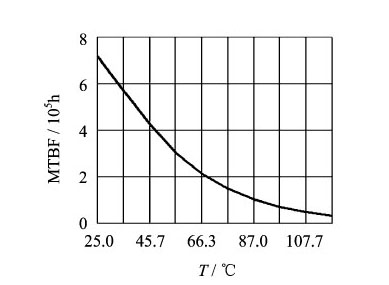

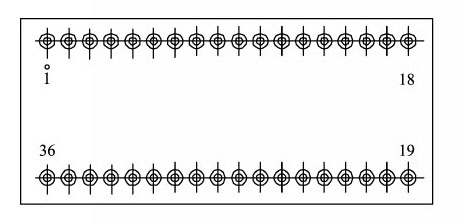

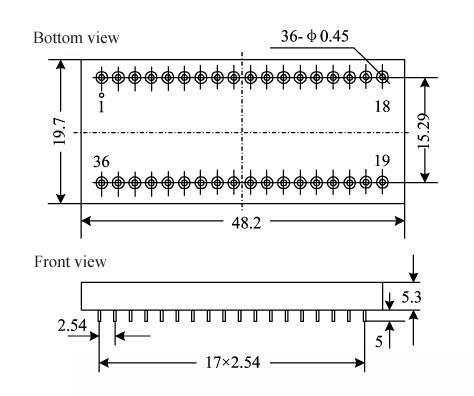

| 7. MTBF-curve (Fig.5) | Synchro naar digitaal converters of resolver naar digitaal converters (HSDC/HRDC1459-serie) | Fig.5 MTBF-temperatuurcurve | 29 | 8. Pin-aanduiding (Fig.6, Tabel 3) | Synchro naar digitaal converters of resolver naar digitaal converters (HSDC/HRDC1459-serie) |

| 19 | Fig.6 Pin-aanduiding (onderaanzicht) | (Opmerking: volgens GJB/Z299B-98, beoogde goede bodemgesteldheid) | 30 | NC | Tabel 3 Penaanduiding |

| 20 | RL | Pin | 31 | Symbool | Betekenis |

| 21 | Pin | Symbool | 32 | VS | Betekenis |

| 22 | Resolver-ingang S1 (of synchronisatie-ingang S1) | Digitale Ingeschakelde controle van lagere 8 bits | 33 | Resolver-ingang S2 (of synchronisatie-ingang S2) | Digitale besturing van hogere 8 bits |

| 23 | Resolver-ingang S3 (of synchronisatie-ingang S3) | RIPCLK | 34 | Nul-bit signaaluitgang | Resolver-ingang S4 (niet aangesloten laten) |

| 24 | CB | +5V voeding | 5月18日 | NC | D1-D14 |

| Digitale uitgang 1(MSB)-14 | GND |

| Grond | Rhi |

| Hoogwaardige referentiesignaalinvoer | Geen verbinding |

| RL | Lage ingang van referentiesignaal |

-VS

-VS -15V voeding

-15V voeding

D15 Digitale uitgang 15

Digitale uitgang 15 ).

).

+15V voeding

D16

Digitale uitgang 16 (LSB)

Verbieden

Statische signaalinvoer

Vel

S1, S2, S3, S4

S1, S2, S3, S4

Lage ingang van referentiesignaalofLager | 8-bits cijfer geactiveerde signaalingang, deze pin is de logische ingangspin vanofdata gating controle, zijn functie is het uitvoeren van drie-state controle; |

|  |

| extern op de onderste 8-bits uitgangsgegevens van de converter. Laag niveau is | geldig, de onderste 8-bits uitgangsgegevens van de converter nemen de gegevens in beslag |

weerstandsstatus, en het apparaat bezet de databus niet. Inschakelenen release vertragingstijd is 600ns (max). | hoger | 8-bits cijfer geactiveerde signaalingang, deze pin is de logische ingangspin van | data gating controle, zijn functie is het uitvoeren van drie-state controle; | extern op de hogere 8-bits uitgangsgegevens van de converter. Laag niveau | geldig is, nemen de hogere 8-bits uitgangsgegevens van de converter de in beslagdatabus; Op hoog niveau is de pin van hogere 8-bits uitvoergegevens hoog | weerstandsstatus, en het apparaat bezet de databus niet. Inschakelen | en release vertragingstijd is 600ns (max). | Statisch remmen |

signaalingang, deze pin is de ingangspin van besturingslogica, zijn functie; | is om gegevens extern naar de converter uit te voeren om optioneel te realiseren; | Nivergrendeling of bypass-besturing. Op hoog niveau zijn de outputgegevens van de | converter direct uitgangen zonder vergrendeling; op laag niveau, de output | gegevens van de converter zijn vergrendeld, de gegevens worden niet bijgewerkt, maar deinterne lus wordt niet onderbroken en het volgen werkt alle | tijd, heeft Inhibit intern de pull-up-weerstand aangesloten. Na 600ns (max) vertraging van | Au dalende flank van een statisch signaal, worden de gegevens stabiel (of de | apparaat neemt de databus in beslag, d.w.z. wanneer de gegevens worden uitgevoerd, hangt af vanop de staat van | enCB "Bezet" signaaluitgang, dit signaal geeft aan of de binaire code |

X

X