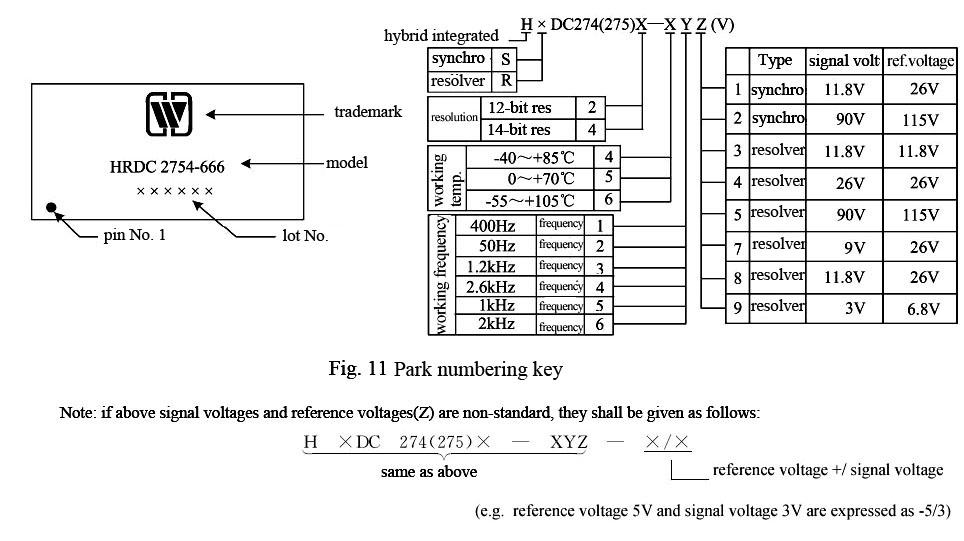

De werkende macht keurt ±15V en + 5V gelijkstroom goed. Er zijn twee soorten uitgangssignalen: drielijns synchro- en referentiesignaal (SDC-converter) of vierlijns resolver en referentiesignaal (RDC-converter); de output keurt parallelle digitale codes van binair systeem goed.

| Resolutie: 12 bits, 14 bits |  |

| Hoge volgsnelheid | |

| Hybride integratie, metalen behuizing | |

| Vergrendelingsuitgang met drie standen | |

| Met snelheidssignaal Vel-uitgang | |

| Onbepaalde compatibiliteit met AD1740-serie |

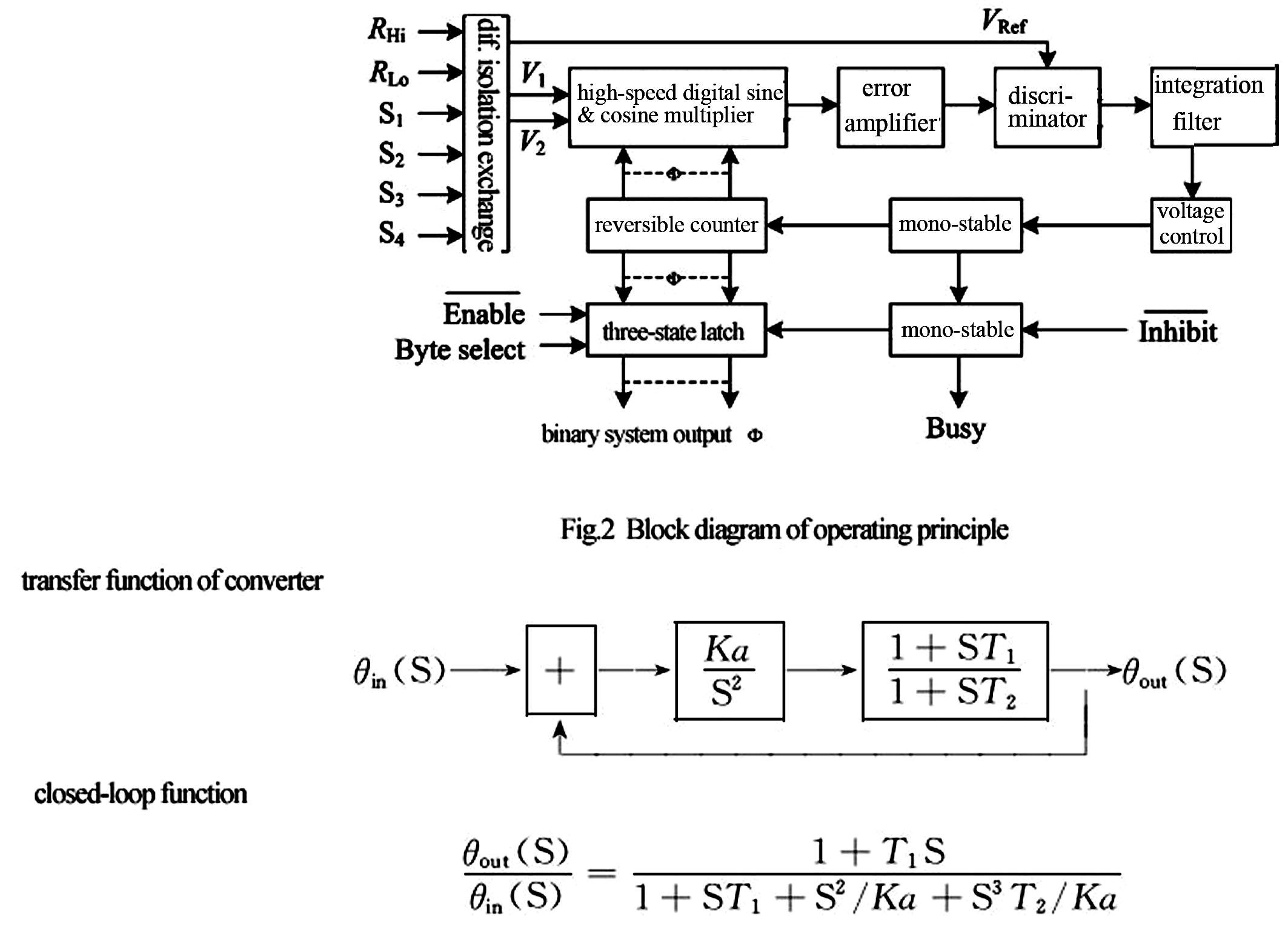

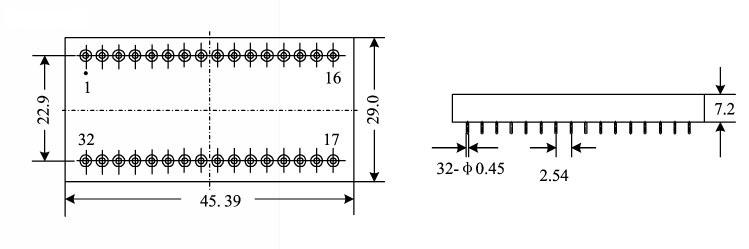

De HSDC/HRDC27-serie is de digitaal-naar-synchro-converters of resolver-naar-digitaal-converters voor het continu volgen van type II servolus, parallel vergrendeld en uitgevoerd met 12-bits of 14-bits natuurlijke binair gecodeerde gegevens met 32-lijns dual-in-line metaal pakket, heeft de voordelen van een klein volume, een laag gewicht en een hoge betrouwbaarheid, enz., Het wordt veel toegepast in een dergelijk automatisch besturingssysteem zoals een radarsysteem, een navigatiesysteem, enz.

De werkende macht keurt ±15V en + 5V gelijkstroom goed. Er zijn twee soorten uitgangssignalen: drielijns synchro- en referentiesignaal (SDC-converter) of vierlijns resolver en referentiesignaal (RDC-converter); de output keurt parallelle digitale codes van binair systeem goed.

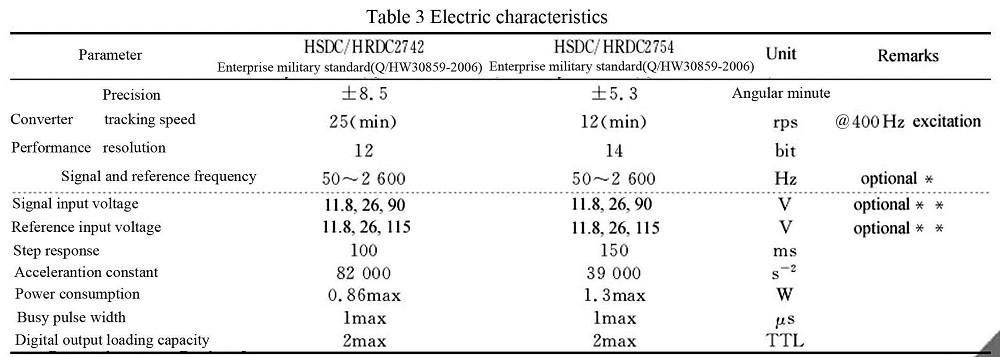

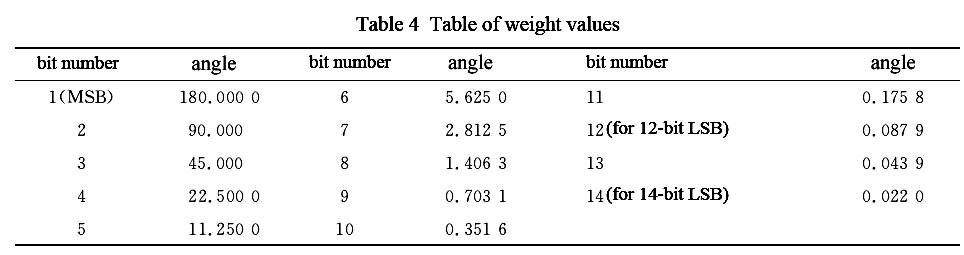

Tabel 2 Nominale voorwaarden en aanbevolen bedrijfsomstandigheden

Absoluut max. nominale waarde | Voedingsspanning Vs: ± 17,5V |

Logische spanning VL: +5,5V | |

Opslagtemperatuurbereik: -55 ~ + 125 | |

Aanbevolen bedrijfsomstandigheden | Voedingsspanning Vs: ± 5V |

Logische spanning VL: 5V | |

Effectieve waarde van referentiespanning VRef: ± 10% van nominale waarde | |

Geldigheid van signaalspanning V1*: ±5% van nominale waarde | |

Referentiefrequentie f*: 50Hz~2.6kHz | |

Bedrijfstemperatuurbereik TA: -40~+85℃,-55~+105℃ |

Opmerking: * geeft aan dat het kan worden aangepast volgens de vereisten van de gebruiker.

| uitgang; lees 12-bits of 14-bits gegevens; stel Inhibit in op logische "1" om: |  |

| 16-bits overdracht). | B: de converter is aangesloten op een 8-bits bus, D1 ~ D8-bits zijn aangesloten op de databus en de rest is leeg. |

| |

| Remmen is | |

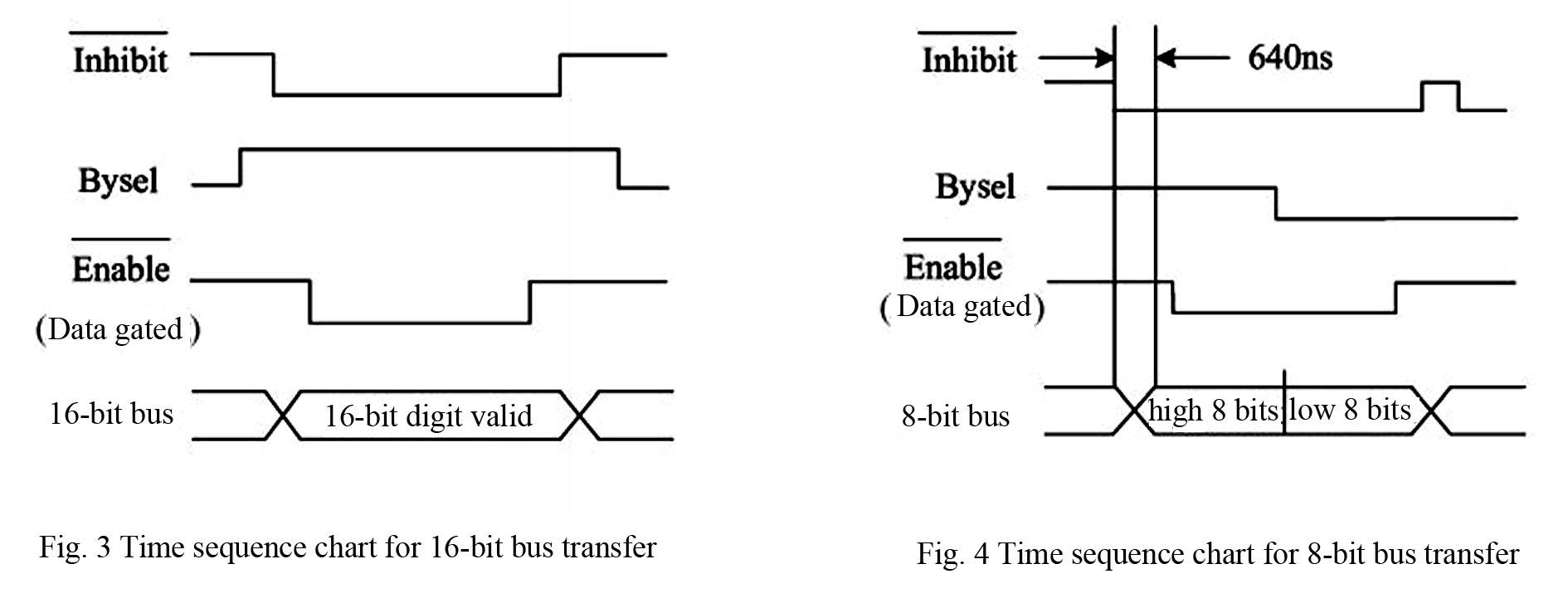

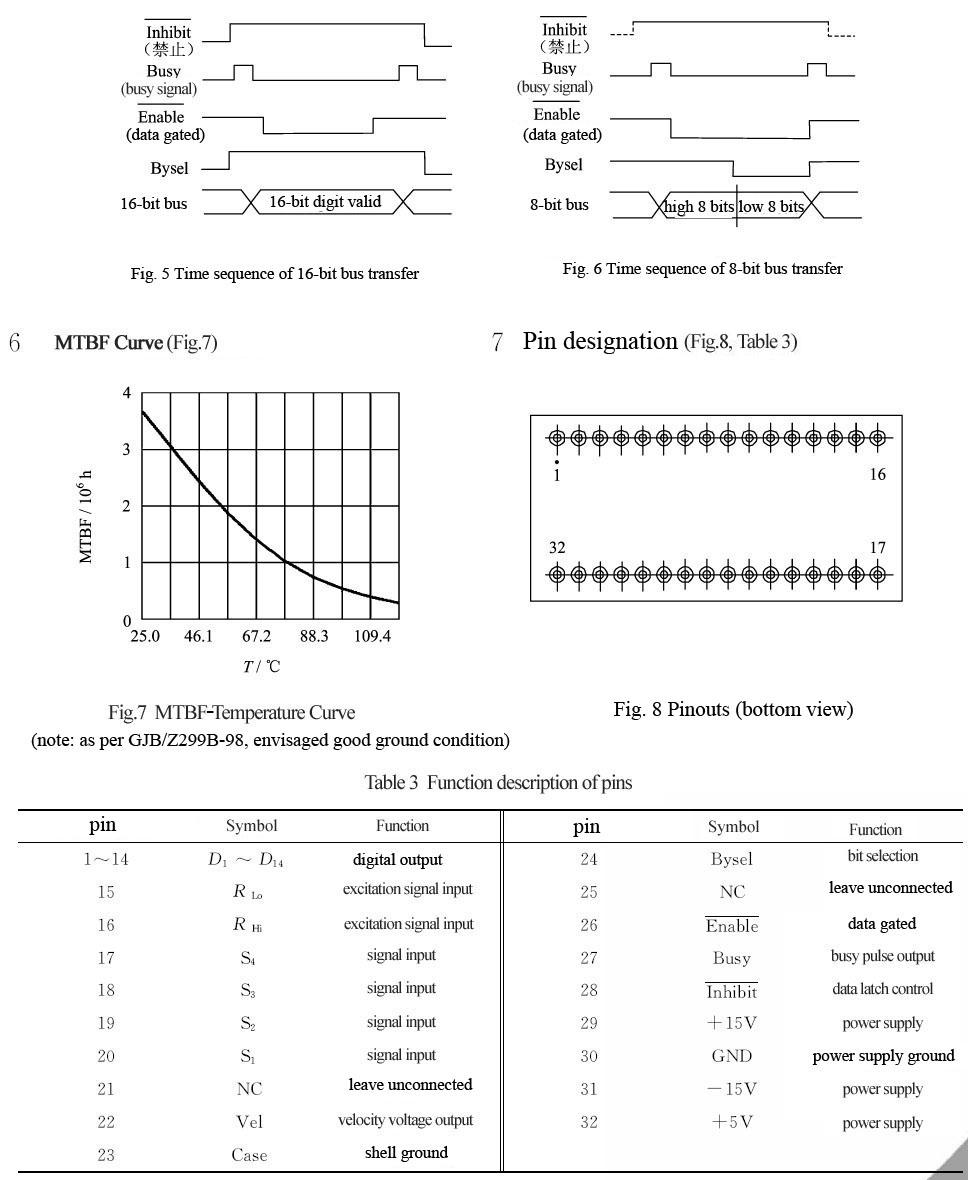

| Schakel in op logische "0", de vergrendelingsgegevens in de converter mogen | uitvoer zijn; als Byse1 is ingesteld op logische "1", leest de converter direct | de hogere 8-bits gegevens, als Byse1 is ingesteld op logisch "0", leest de converter | de rest bits, voegt automatisch nul toe voor onvolledige bits; stel Inhibit data locking control (Inhibit signal) in op logisch "1" om gereed te zijn voor het lezen van de volgende geldige gegevens (zie Fig. 3 en Fig. 4 voor 8-bit overdrachtstijdreeks) | (2) Drukke methode (asynchroon lezen): | In de asynchrone leesmodus is Inhibit data locking control (Inhibit signaal) ingesteld op logisch "1" of leeg, ongeacht of de interne lus altijd in staat is | de stabiele toestand of dat de uitvoergegevens geldig zijn, wordt bepaald | via de bezettoon Bezet. Wanneer het bezet-signaal hoog is | niveau, het geeft aan dat de gegevens worden geconverteerd, en de gegevens op dit |

| tijd is onstabiel en ongeldig; wanneer het bezet-signaal op een laag niveau staat, | geeft aan dat de gegevensconversie is voltooid, en de gegevens op dit | Au | tijd is stabiel en geldig. Zodra een hoog niveau optreedt in Bezet tijdens het lezen, | Au | de lezing van deze tijd is ongeldig. In asynchrone leesmodus, Bezet | Au | output is pulstrein van TTL-niveau, de breedte tussen is gerelateerd aan: | rotatiesnelheid. Evenzo zijn er ook 8-bits en 16-bits voor twee gebruik |

X

X